# C H A P T E R

# Machines with Memory

As we saw in Chapter 1, every finite computational task can be realized by a combinational circuit. While this is an important concept, it is not very practical; we cannot afford to design a special circuit for each computational task. Instead we generally perform computational tasks with machines having memory. In a strong sense to be explored in this chapter, the memory of such machines allows them to reuse their equivalent circuits to realize functions of high circuit complexity.

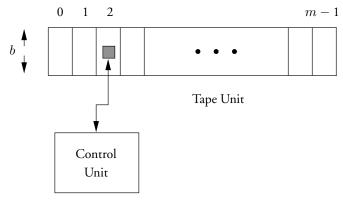

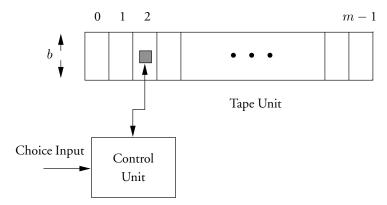

In this chapter we examine the deterministic and nondeterministic finite-state machine (FSM), the random-access machine (RAM), and the Turing machine. The finite-state machine moves from state to state while reading input and producing output. The RAM has a central processing unit (CPU) and a random-access memory with the property that each memory word can be accessed in one unit of time. Its CPU executes instructions, reading and writing data from and to the memory. The Turing machine has a control unit that is a finite-state machine and a tape unit with a head that moves from one tape cell to a neighboring one in each unit of time. The control unit reads from, writes to, and moves the head of the tape unit.

We demonstrate through simulation that the RAM and the Turing machine are universal in the sense that every finite-state machine can be simulated by the RAM and that it and the Turing machine can simulate each other. Since they are equally powerful, either can be used as a reference model of computation.

We also simulate with circuits computations performed by the FSM, RAM, and Turing machine. These circuit simulations establish two important results. First, they show that all computations are constrained by the available resources, such as space and time. For example, if a function f is computed in T steps by the RAM with storage capacity S (in bits), then S and T must satisfy the inequality  $C_{\Omega}(f) = O(ST)$ , where  $C_{\Omega}(f)$  is the size of the smallest circuit for f over the complete basis  $\Omega$ . Any attempt to compute f on the RAM using space S and time T whose product is too small will fail. Second, an  $O(\log ST)$ -space, O(ST)-time program exists to write the descriptions of circuits simulating the above machines. This fact leads to the identification in this chapter of the first examples of **P**-complete and **NP**-complete problems.

#### 3.1 Finite-State Machines

The finite-state machine (FSM) has a set of states, one of which is its initial state. At each unit of time an FSM is given a letter from its input alphabet. This causes the machine to move from its current state to a potentially new state. While in a state, the FSM produces a letter from its output alphabet. Such a machine computes the function defined by the mapping from its initial state and strings of input letters to strings of output letters. FSMs can also be used to accept strings, as discussed in Chapter 4. Some states are called final states. A string is recognized (or accepted) by an FSM if the last state entered by the machine on that input string is a final state. The language recognized (or accepted) by an FSM is the set of strings accepted by it. We now give a formal definition of an FSM.

**DEFINITION 3.1.1** A finite-state machine (FSM) M is a seven-tuple  $M = (\Sigma, \Psi, Q, \delta, \lambda, s, F)$ , where  $\Sigma$  is the input alphabet,  $\Psi$  is the output alphabet, Q is the finite set of states,  $\delta: Q \times \Sigma \mapsto Q$  is the next-state function,  $\lambda: Q \mapsto \Psi$  is the output function, s is the initial state (which may be fixed or variable), and F is the set of final states ( $F \subseteq Q$ ). If the FSM is given input letter a when in state q, it enters state  $\delta(q, a)$ . While in state q it produces the output letter  $\lambda(q)$ .

The FSM M accepts the string  $w \in \Sigma^*$  if the last state entered by M on the input string w starting in state s is in the set F. M recognizes (or accepts) the language L consisting of the set of such strings.

When the initial state of the FSM M is not fixed, for each integer T M maps the initial state s and its T external inputs  $\mathbf{w}_1, \mathbf{w}_2, \ldots, \mathbf{w}_T$  onto its T external outputs  $\mathbf{y}_1, \mathbf{y}_2, \ldots, \mathbf{y}_T$  and the final state  $q^{(T)}$ . We say that in T steps the FSM M computes the function  $f_M^{(T)}: Q \times \Sigma^T \mapsto Q \times \Psi^T$ . It is assumed that the sets  $\Sigma$ ,  $\Psi$ , and Q are encoded in binary so that  $f_M^{(T)}$  is a binary function.

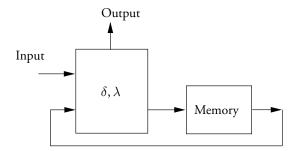

The next-state and output functions of an FSM,  $\delta$  and  $\lambda$ , can be represented as in Fig. 3.1. We visualize these functions taking a state value from a memory and an input value from an external input and producing next-state and output values. Next-state values are stored in the memory and output values are released to the external world. From this representation an actual machine (a sequential circuit) can be constructed (see Section 3.3). Once circuits are constructed for  $\delta$  and  $\lambda$ , we need only add memory units and a clock to construct a sequential circuit that emulates an FSM.

Figure 3.1 The finite-state machine model.

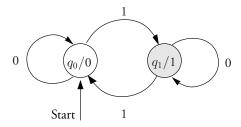

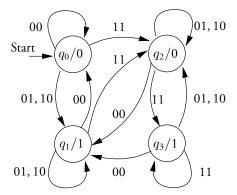

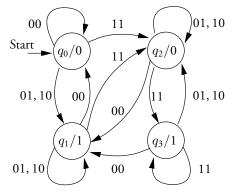

Figure 3.2 A finite-state machine computing the EXCLUSIVE OR of its inputs.

An example of an FSM is shown in Fig. 3.2. Its input and output alphabets and state sets are  $\Sigma = \{0, 1\}$ ,  $\Psi = \{0, 1\}$ , and  $Q = \{q_0, q_1\}$ , respectively. Its next-state and output functions,  $\delta$  and  $\lambda$ , are given below.

| q     | $\sigma$ | $\delta(q,\sigma)$ | q     | $\lambda(q)$ |

|-------|----------|--------------------|-------|--------------|

| $q_0$ | 0        | $q_0$              | $q_0$ | 0            |

| $q_0$ | 1        | $q_1$              | $q_1$ | 1            |

| $q_1$ | 0        | $q_1$              |       |              |

| $q_1$ | 1        | $q_0$              |       |              |

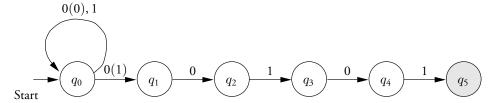

The FSM has initial state  $q_0$  and final state  $q_1$ . As a convenience we explicitly identify final states by shading, although in practice they can be associated with states producing a particular output letter.

Each state has a label  $q_j/v_j$ , where  $q_j$  is the name of the state and  $v_j$  is the output produced while in this state. The initial state has an arrow labeled with the word "start" pointing to it. Clearly, the set of strings accepted by this FSM are those containing an odd number of instances of 1. Thus it computes the EXCLUSIVE OR function on an arbitrary number of inputs.

While it is conventional to think of the finite-state machine as a severely restricted computational model, it is actually a very powerful one. The random-access machine (RAM) described in Section 3.4 is an FSM when the number of memory locations that it contains is bounded, as is always so in practice. When a program is first placed in the memory of the RAM, the program sets the initial state of the RAM. The RAM, which may or may not read external inputs or produce external outputs, generally will leave its result in its memory; that is, the result of the computation often determines the final state of the random-access machine.

The FSM defined above is called a **Moore machine** because it was defined by E.F. Moore [222] in 1956. An alternative FSM, the **Mealy machine** (defined by Mealy [214] in 1955), has an output function  $\lambda^*: Q \times \Sigma \mapsto \Psi$  that generates an output on each transition from one state to another. This output is determined by both the state in which the machine resides before the state transition and the input letter causing the transition. It can be shown that the two machine models are equivalent (see Problem 3.6): any computation one can do, the other can do also.

#### 3.1.1 Functions Computed by FSMs

We now examine the ways in which an FSM might compute a function. Since our goal is to understand the power and limits of computation, we must be careful not to assume that an FSM can have hidden access to an external computing device. All computing devices must be explicit. It follows that we allow FSMs only to compute functions that receive inputs and produce outputs at data-independent times.

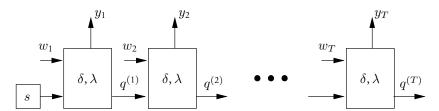

To understand the function computed by an FSM M, observe that in initial state  $q^{(0)} = s$  and receiving input letter  $w_1$ , M enters state  $q^{(1)} = \delta(q^{(0)}, w_1)$  and produces output  $y_1 = \lambda(q^{(1)})$ . If M then receives input  $w_2$ , it enters state  $q^{(2)} = \delta(q^{(1)}, w_2)$  and produces output  $y_2 = \lambda(q^{(2)})$ . Repeated applications of the functions  $\delta$  and  $\lambda$  on successive states with successive inputs, as suggested by Fig. 3.3, generate the outputs  $y_1, y_2, \ldots, y_T$  and the final state  $q^{(T)}$ . The function  $f_M^{(T)}: Q \times \Sigma^T \mapsto Q \times \Psi^T$  given in Definition 3.1.1 defines this mapping from an initial state and inputs to the final state and outputs:

$$f_M^{(T)}\left(q^{(0)}, w_1, w_2, \dots, w_T\right) = \left(q^{(T)}, y_1, y_2, \dots, y_T\right)$$

This simulation of a machine with memory by a circuit illustrates a fundamental point about computation, namely, that the role of memory is to hold intermediate results on which the logical circuitry of the machine can operate in successive cycles.

When an FSM M is used in a T-step computation, it usually does not compute the most general function  $f_M^{(T)}$  that it can. Instead, some restrictions are generally placed on the possible initial states, on the values of the external inputs provided to M, and on the components of the final state and output letters used in the computation. Consider three examples of the specialization of an FSM to a particular task. In the first, let the FSM model be that shown in Fig. 3.2 and let it be used to form the EXCLUSIVE OR of n variables. In this case, we supply n bits to the FSM but ignore all but the last output value it produces. In the second example, let the FSM be a programmable machine in which a program is loaded into its memory before the start of a computation, thereby setting its initial state. The program ignores all external inputs and produces no output, leaving the value of the function in memory. In the third example, again let the FSM be programmable, but let the program that resides initially residing in its memory be a "boot program" that treats its inputs as program statements. (Thus, the FSM has a fixed initial state.) The boot program forms a program by loading these statements into successive memory locations. It then jumps to the first location in this program.

In each of these examples, the function f that is actually computed by M in T steps is a subfunction of the function  $f_M^{(T)}$  because f is obtained by either restricting the values of

**Figure 3.3** A circuit computing the same function,  $f_M^{(T)}$ , as a finite-state machine M in T steps.

the initial state and inputs to M or deleting outputs or both. We assume that every function computed by M in T steps is a subfunction f of the function  $f_M^{(T)}$ .

The simple construction of Fig. 3.3 is the first step in deriving a space-time product inequality for the random-access machine in Section 3.5 and in establishing a connection between Turing time and circuit complexity in Section 3.9.2. It is also involved in the definition of the **P**-complete and **NP**-complete problems in Section 3.9.4.

#### 3.1.2 Computational Inequalities for the FSM

In this book we model each computational task by a function that, we assume without loss of generality, is binary. We also assume that the function  $f_M^{(T)}:Q\times \Sigma^T\mapsto Q\times \Psi^T$  computed in T steps by an FSM M is binary. In particular, we assume that the next-state and output functions,  $\delta$  and  $\lambda$ , are also binary; that is, we assume that their input, state, and output alphabets are encoded in binary. We now derive some consequences of the fact that a computation by an FSM can be simulated by a circuit.

The size  $C_{\Omega}\left(f_{M}^{(T)}\right)$  of the smallest circuit to compute the function  $f_{M}^{(T)}$  is no larger than the size of the circuit shown in Fig. 3.3. But this circuit has size  $T\cdot C_{\Omega}(\delta,\lambda)$ , where  $C_{\Omega}(\delta,\lambda)$  is the size of the smallest circuit to compute the functions  $\delta$  and  $\lambda$ . The depth of the shallowest circuit for  $f_{M}^{(T)}$  is no more than  $T\cdot D_{\Omega}(\delta,\lambda)$  because the longest path through the circuit of Fig. 3.3 has this length.

Let f be the function computed by M in T steps. Since it is a subfunction of  $f_M^{(T)}$ , it follows from Lemma 2.4.1 that the size of the smallest circuit for f is no larger than the size of the circuit for  $f_M^{(T)}$ . Similarly, the depth of f,  $D_{\Omega}(f)$ , is no more than that of  $f_M^{(T)}$ . Combining the observations of this paragraph with those of the preceding paragraph yields the following computational inequalities. A **computational inequality** is an inequality relating parameters of computation, such as time and the circuit size and depth of the next-state and output function, to the size or depth of the smallest circuit for the function being computed.

**THEOREM 3.1.1** Let  $f_M^{(T)}$  be the function computed by the FSM  $M=(\Sigma, \Psi, Q, \delta, \lambda, s, F)$  in T steps, where  $\delta$  and  $\lambda$  are the binary next-state and output functions of M. The circuit size and depth over the basis  $\Omega$  of any function f computed by M in T steps satisfy the following inequalities:

$$C_{\Omega}(f) \leq C_{\Omega}\left(f_{M}^{(T)}\right) \leq TC_{\Omega}(\delta, \lambda)$$

$D_{\Omega}(f) \leq D_{\Omega}\left(f_{M}^{(T)}\right) \leq TD_{\Omega}(\delta, \lambda)$

The circuit size  $C_{\Omega}(\delta,\lambda)$  and depth  $D_{\Omega}(\delta,\lambda)$  of the next-state and output functions of an FSM M are measures of its complexity, that is, of how useful they are in computing functions. The above theorem, which says nothing about the actual technologies used to realize M, relates these two measures of the complexity of M to the complexities of the function f being computed. This is a theorem about computational complexity, not technology.

These inequalities stipulate constraints that must hold between the time T and the circuit size and depth of the machine M if it is used to compute the function f in T steps. Let the product  $TC_{\Omega}(\delta, \lambda)$  be defined as the **equivalent number of logic operations performed by** M. The first inequality of the above theorem can be interpreted as saying that the number of equivalent logic operations performed by an FSM to compute a function f must be at least

the minimum number of gates necessary to compute f with a circuit. A similar interpretation can be given to the second inequality involving circuit depth.

The first inequality of Theorem 3.1.1 and the interpretation given to  $T \cdot C_{\Omega}(\delta, \lambda)$  justify the following definitions of computational work and power. Here power is interpreted as the time rate at which work is done. These measures correlate nicely with our intuition that machines that contain more equivalent computing elements are more powerful.

**DEFINITION 3.1.2** The computational work done by an FSM  $M = (\Sigma, \Psi, Q, \delta, \lambda, s, F)$  is  $TC_{\Omega}(\delta, \lambda)$ , the number of equivalent logical operations performed by M, which is the product of T, the number of steps executed by M, and  $C_{\Omega}(\delta, \lambda)$ , the size complexity of its next-state and output functions. The **power** of an FSM M is  $C_{\Omega}(\delta, \lambda)$ , the number of logical operations performed by M per step.

Theorem 3.1.1 is also a form of **impossibility theorem**: it is impossible to compute functions f for which  $TC_{\Omega}(\delta,\lambda)$  and  $TD_{\Omega}(\delta,\lambda)$  are respectively less than the size and depth complexity of f. It may be possible to compute a function on some points of its domain with smaller values of these parameters, but not on all points. The halting problem, another example of an impossibility theorem, is presented in Section 5.8.2. However, it deals with the computation of functions over infinite domains.

The inequalities of Theorem 3.1.1 also place upper limits on the size and depth complexities of functions that can be computed in a bounded number of steps by an FSM, regardless of how the FSM performs the computation.

Note that there is no guarantee that the upper bounds stated in Theorem 3.1.1 are at all close to the lower bounds. It is always possible to compute a function inefficiently, that is, with resources that are greater than the minimal resources necessary.

#### 3.1.3 Circuits Are Universal for Bounded FSM Computations

We now ask whether the classes of functions computed by circuits and by FSMs executing a bounded number of steps are different. We show that they are the same. Many different functions can be computed from the function  $f_M^{(T)}$  by specializing inputs and/or deleting outputs.

**THEOREM 3.1.2** Every subfunction of the function  $f_M^{(n)}$  computable by an FSM on n inputs is computable by a Boolean circuit and vice versa.

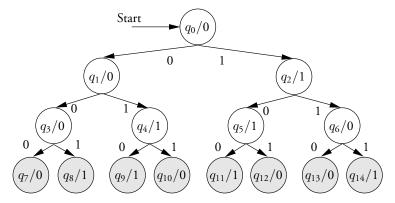

**Proof** A Boolean function on n inputs, f, may be computed by an FSM with  $2^{n+1} - 1$  states by branching from the current state to one of two different states on inputs 0 and 1 until all n inputs have been read; it then produces the output that would be produced by f on these n inputs. A fifteen-state version of this machine that computes the EXCLUSIVE OR on three inputs as a subfunction is shown in Fig. 3.4.

The proof in the other direction is also straightforward, as described above and represented schematically in Fig. 3.3. Given a binary representation of the input, output, and state symbols of an FSM, their associated next-state and output functions are binary functions. They can be realized by circuits, as can  $f_M^{(n)}(s, \boldsymbol{w}) = (q^{(n)}, \boldsymbol{y})$ , the function computed by the FSM on n inputs, as suggested by Fig. 3.3. Finally, the subfunction f is obtained by fixing the appropriate inputs, assigning variable names to the remaining inputs, and deleting the appropriate outputs.

**Figure 3.4** A fifteen-state FSM that computes the EXCLUSIVE OR of three inputs as a subfunction of  $f_M^{(3)}$  obtained by deleting all outputs except the third.

#### 3.1.4 Interconnections of Finite-State Machines

Later in this chapter we examine a family of FSMs characterized by a computational unit connected to storage devices of increasing size. The random-access machine that has a CPU of small complexity and a random-access memory of large but indeterminate size is of this type. The Turing machine having a fixed control unit that moves a tape head over a potentially infinite tape is another example.

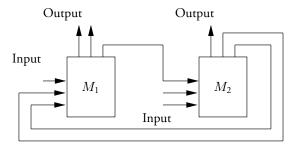

This idea is captured by the **interconnection of synchronous FSMs**. Synchronous FSMs read inputs, advance from state to state, and produce outputs in synchronism. We allow two or more synchronous FSMs to be interconnected so that some outputs from one FSM are supplied as inputs of another, as illustrated in Fig. 3.5. Below we generalize Theorem 3.1.1 to a pair of synchronous FSMs. We model random-access machines and Turing machines in this fashion when each uses a finite amount of storage.

**THEOREM 3.1.3** Let  $f_{M_1 \times M_2}^{(T)}$  be a function computed in T steps by a pair of interconnected synchronous FSMs,  $M_1 = (\Sigma_1, \Psi_1, Q_1, \delta_1, \lambda_1, s_1, F_1)$  and  $M_2 = (\Sigma_2, \Psi_2, Q_2, \delta_2, \lambda_2, s_2, F_2)$ .

**Figure 3.5** The interconnection of two finite-state machines in which one of the three outputs of  $M_1$  is supplied as an input to  $M_2$  and two of the three outputs of  $M_2$  are supplied to  $M_1$  as inputs.

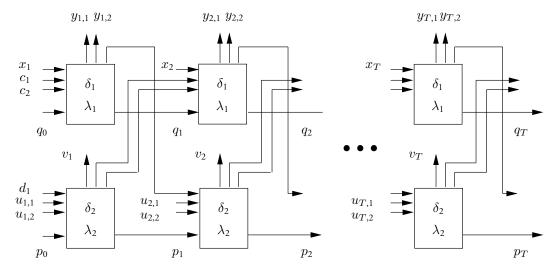

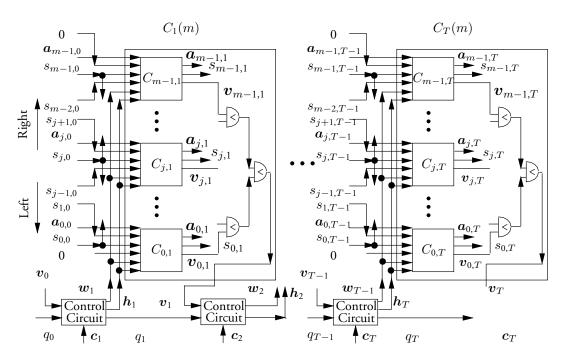

**Figure 3.6** A circuit simulating T steps of the two synchronous interconnected FSMs shown in Fig. 3.5. The top row of circuits simulates a T-step computation by  $M_1$  and the bottom row simulates a T-step computation by  $M_2$ . One of the three outputs of  $M_1$  is supplied as an input to  $M_2$  and two of the three outputs of  $M_2$  are supplied to  $M_1$  as inputs. The states of  $M_1$  on the initial and T successive steps are  $q_0, q_1, \ldots, q_T$ . Those of  $M_2$  are  $p_0, p_1, \ldots, p_T$ .

Let  $C_{\Omega}(\delta, \lambda)$  and  $D_{\Omega}(\delta, \lambda)$  be the size and depth of encodings of the next-state and output functions. Then, the circuit size and depth over the basis  $\Omega$  of any function f computed by the pair  $M_1 \times M_2$  in T steps (that is, a subfunction of  $f_{M_1 \times M_2}^{(T)}$ ) satisfy the following inequalities:

$$C_{\Omega}(f) \leq T[C_{\Omega}(\delta_1, \lambda_1) + C_{\Omega}(\delta_2, \lambda_2)]$$

$$D_{\Omega}(f) \leq T[\max(D_{\Omega}(\delta_1, \lambda_1), D_{\Omega}(\delta_2, \lambda_2))]$$

**Proof** The construction that leads to this result is suggested by Fig. 3.6. We unwind both FSMs and connect the appropriate outputs from one to the other to produce a circuit that computes  $f_{M_1 \times M_2}^{(T)}$ . Observe that the number of gates in the simulated circuit is T times the sum of the number of gates, whereas the depth is T times the depth of the deeper circuit.

#### 3.1.5 Nondeterministic Finite-State Machines

The finite-state machine model described above is called a **deterministic FSM** (DFSM) because, given a current state and an input, the next state of the FSM is uniquely determined. A potentially more general FSM model is the **nondeterministic** FSM (NFSM) characterized by the possibility that several next states can be reached from the current state for some given input letter.

One might ask if such a model has any use, especially since to the untrained eye a nondeterministic machine would appear to be a dysfunctional deterministic one. The value of an NFSM is that it may recognize languages with fewer states and in less time than needed by a DFSM. The concept of nondeterminism will be extended later to the Turing machine, where it is used to classify languages in terms of the time and space they need for recognition. For example, it will be used to identify the class **NP** of languages that are recognized by nondeterministic Turing machines in a number of steps that is polynomial in the length of their inputs. (See Section 3.9.6.) Many important combinatorial problems, such as the traveling salesperson problem, fall into this class.

The formal definition of the NFSM is given in Section 4.1, where the next-state function  $\delta: Q \times \Sigma \mapsto Q$  of the FSM is replaced by a next-state function  $\delta: Q \times \Sigma \mapsto 2^Q$ . Such functions assign to each state q and input letter a a subset  $\delta(q,a)$  of the set Q of states of the NFSM ( $2^Q$ , the power set, is the set of all subsets of Q. It is introduced in Section 1.2.1.) Since the value of  $\delta(q,a)$  can be the empty set, there may be no successor to the state q on input a. Also, since  $\delta(q,a)$  when viewed as a set can contain more than one element, a state q can have edges labeled a to several other states. Since a DFSM has a single successor to each state on every input, a DFSM is an NFSM in which  $\delta(q,a)$  is a singleton set.

While a DFSM M accepts a string w if w causes M to move from the initial state to a final state in F, an NFSM accepts w if there is some set of next-state choices for w that causes M to move from the initial state to a final state in F.

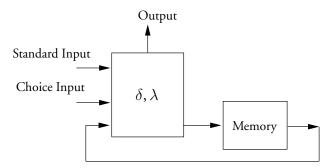

An NFSM can be viewed as a purely deterministic finite-state machine that has two inputs, as suggested in Fig. 3.7. The first, the **standard input**, a, accepts the user's data. The second, the **choice input**, c, is used to choose a successor state when there is more than one. The information provided via the choice input is not under the control of the user supplying data via the standard input. As a consequence, the machine is nondeterministic from the point of view of the user but fully deterministic to an outside observer. It is assumed that the **choice agent** supplies the choice input and, with full knowledge of the input to be provided by the user, chooses state transitions that, if possible, lead to acceptance of the user input. On the other hand, the choice agent cannot force the machine to accept inputs for which it is not designed.

In an NFSM it is not required that a state q have a successor for each value of the standard and choice inputs. This possibility is captured by allowing  $\delta(q,a,c)$  to have no value, denoted by  $\delta(q,a,c)=\bot$ .

Figure 3.8 shows an NFSM that recognizes strings over  $\mathcal{B}^*$  that end in 00101. In this figure parentheses surround the choice input when its value is needed to decide the next state. In this machine the choice input is set to 1 when the choice agent knows that the user is about to supply the suffix 00101.

**Figure 3.7** A nondeterministic finite-state machine modeled as a deterministic one that has a second choice input whose value disambiguates the value of the next state.

**Figure 3.8** A nondeterministic FSM that accepts binary strings ending in 00101. Choice inputs are shown in parentheses for those user inputs for which the value of choice inputs can disambiguate next-state moves.

**Figure 3.9** An example of an NFSM whose choice agent (its values are in parentheses) accepts not only strings in a language L, but all strings.

Although we use the anthropomorphic phrase "choice agent," it is important to note that this choice agent cannot freely decide which strings to accept and which not. Instead, it must when possible make choices leading to acceptance. Consider, for example, the machine in Fig. 3.9. It would appear that its choice agent can accept strings in an arbitrary language L. In fact, the language that it accepts contains all strings.

Given a string w in the language L accepted by an NFSM, a choice string that leads to its acceptance is said to be a **succinct certificate** for its membership in L.

It is important to note that the nondeterministic finite-state machine is not a model of reality, but is used instead primarily to classify languages. In Section 4.1 we explore the language-recognition capability of the deterministic and nondeterministic finite-state machines and show that they are the same. However, the situation is not so clear with regard to Turing machines that have access to unlimited storage capacity. In this case, we do not know whether or not the set of languages accepted in polynomial time on deterministic Turing machines (the class **P**) is the same set of languages that is accepted in polynomial time by nondeterministic Turing machines (the class **NP**).

# 3.2 Simulating FSMs with Shallow Circuits\*

In Section 3.1 we demonstrated that every T-step FSM computation can be simulated by a circuit whose size and depth are both O(T). In this section we show that every T-step finite-state machine computation can be simulated by a circuit whose size and depth are O(T) and  $O(\log T)$ , respectively. While this seems a serious improvement in the depth bound, the coefficients hidden in the big-O notation for both bounds depend on the number of states of the FSM and can be very large. Nevertheless, for simple problems, such as binary addition, the

**Figure 3.10** A finite-state machine that adds two binary numbers. Their two least significant bits are supplied first followed by those of increasing significance. The output bits represent the sum of the two numbers.

results of this section can be useful. We illustrate this here for binary addition by exhibiting small and shallow circuits for the adder FSM of Fig. 3.10. The circuit simulation for this FSM produces the carry-lookahead adder circuit of Section 2.7. In this section we use matrix multiplication, which is covered in Chapter 6.

The new method is based on the representation of the function  $f_M^{(T)}: Q \times \Sigma^T \mapsto Q \times \Psi^T$  computed in T steps by an FSM  $M = (\Sigma, \Psi, Q, \delta, \lambda, s, F)$  in terms of the set of **state-to-state mappings**  $S = \{h: Q \mapsto Q\}$  where S contains the mappings  $\{\Delta_x: Q \mapsto Q \mid x \in \Sigma\}$  and  $\Delta_x$  is defined below.

$$\Delta_x(q) = \delta(q, x) \tag{3.1}$$

That is,  $\Delta_x(q)$  is the state to which state q is carried by the input letter x.

The FSM shown in Fig. 3.10 adds two binary numbers sequentially by simulating a ripple adder. (See Section 2.7.) Its input alphabet is  $\mathcal{B}^2$ , that is, the set of pairs of 0's and 1's. Its output alphabet is  $\mathcal{B}$  and its state set is  $Q = \{q_0, q_1, q_2, q_3\}$ . (A sequential circuit for this machine is designed in Section 3.3.) It has the state-to-state mappings shown in Fig. 3.11.

Let  $\odot: S^2 \mapsto S$  be the operator defined on the set S of state-to-state mappings where for arbitrary  $h_1, h_2 \in S$  and state  $q \in Q$  the operator  $\odot$  is defined as follows:

$$(h_1 \odot h_2)(q) = h_2(h_1(q)) \tag{3.2}$$

|                         |       | q     | $\Delta_{0,1}(q)$ | q     | $\Delta_{1,0}(q)$ | q     | $\Delta_{1,1}(q)$ |

|-------------------------|-------|-------|-------------------|-------|-------------------|-------|-------------------|

| $q_0$ $q_1$ $q_2$ $q_3$ | $q_0$ | $q_0$ |                   | $q_0$ | $q_1$             |       | $q_2$             |

| $q_1$                   | $q_0$ | $q_1$ | $q_1$             | $q_1$ | $q_1$             | $q_1$ | $q_2$             |

| $q_2$                   | $q_1$ |       | $q_2$             | $q_2$ | $q_2$             |       | $q_3$             |

| $q_3$                   | $q_1$ | $q_3$ | $q_2$             | $q_3$ | $q_2$             | $q_3$ | $q_3$             |

Figure 3.11 The state-to-state mappings associated with the FSM of Fig. 3.10.

The state-to-state mappings in S will be obtained by composing the mappings  $\{\Delta_x:Q\mapsto Q\,|\,x\in\Sigma\}$  using this operator.

Below we show that the operator  $\odot$  is **associative**, that is,  $\odot$  satisfies the property  $(h_1 \odot h_2) \odot h_3 = h_1 \odot (h_2 \odot h_3)$ . This means that for each  $q \in Q$ ,  $((h_1 \odot h_2) \odot h_3)(q) = (h_1 \odot (h_2 \odot h_3))(q) = h_3(h_2(h_1(q)))$ . Applying the definition of  $\odot$  in Equation (3.2), we have the following for each  $q \in Q$ :

$$((h_1 \odot h_2) \odot h_3)(q) = h_3((h_1 \odot h_2)(q))$$

$$= h_3(h_2(h_1(q)))$$

$$= (h_2 \odot h_3)(h_1(q))$$

$$= (h_1 \odot (h_2 \odot h_3))(q)$$

(3.3)

Thus,  $\odot$  is associative and  $(S, \odot)$  is a semigroup. (See Section 2.6.) It follows that a prefix computation can be done on a sequence of state-to-state mappings.

We now use this observation to construct a shallow circuit for the function  $f_M^{(T)}$ . Let  $w = (w_1, w_2, \ldots, w_T)$  be a sequence of T inputs to M where  $w_j$  is supplied on the jth step. Let  $q^{(j)}$  be the state of M after receiving the jth input. From the definition of  $\odot$  it follows that  $q^{(j)}$  has the following value where s is the initial state of M:

$$q^{(j)} = (\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j})(s)$$

The value of  $f_M^{(T)}$  on initial state s and T inputs can be represented in terms of  $\mathbf{q}=(q^{(1)},\ldots,q^{(T)})$  as follows:

$$f_M^{(T)}(s, \boldsymbol{w}) = \left(q^{(n)}, \lambda(q^{(1)}), \lambda(q^{(2)}), \dots, \lambda(q^{(T)})\right)$$

Let  $\Lambda^{(T)}$  be the following sequence of state-to-state mappings:

$$\boldsymbol{\Lambda^{(T)}} = (\Delta_{w_1}, \Delta_{w_2}, \dots, \Delta_{w_m})$$

It follows that q can be obtained by computing the state-to-state mappings  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$ ,  $1 \leq j \leq T$ , and applying them to the initial state s. Because  $\odot$  is associative, these T state-to-state mappings are produced by the prefix operator  $\mathcal{P}^{(T)}_{\odot}$  on the sequence  $\Lambda^{(T)}$  (see Theorem 2.6.1):

$$\mathcal{P}_{\odot}^{(T)}(\boldsymbol{\Lambda^{(T)}}) = (\Delta_{w_1}, (\Delta_{w_1} \odot \Delta_{w_2}), \dots, (\Delta_{w_1} \odot \Delta_{w_2} \odot \dots \odot \Delta_{w_T}))$$

Restating Theorem 2.6.1 for this problem, we have the following result.

**THEOREM 3.2.1** For  $T=2^k$ , k an integer, the T state-to-state mappings defined by the T inputs to an FSM M can be computed by a circuit over the basis  $\Omega=\{\odot\}$  whose size and depth satisfy the following bounds:

$$C_{\Omega}\left(\mathcal{P}_{\odot}^{(T)}\right) \le 2T - \log_2 T - 2$$

$D_{\Omega}\left(\mathcal{P}_{\odot}^{(T)}\right) \le 2\log_2 T$

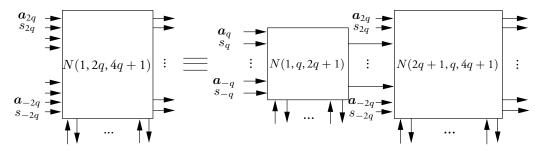

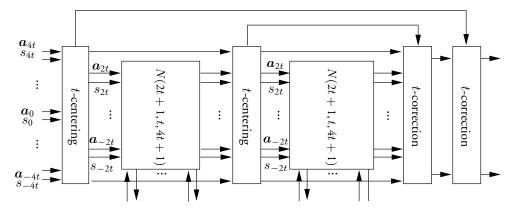

The construction of a shallow Boolean circuit for  $f_M^{(T)}$  is reduced to a five-step problem: 1) for each input letter x design a circuit whose input and output are representations of states and which defines the state-to-state mapping  $\Delta_x$  for input letter x; 2) construct a circuit for the associative operator  $\odot$  that accepts the representations of two state-to-state mappings  $\Delta_y$  and  $\Delta_z$  and produces a representation for the state-to-state mapping  $\Delta_y \odot \Delta_z$ ; 3) use the circuit for  $\odot$  in a parallel prefix circuit to produce the T state-to-state mappings; 4) construct a circuit that combines the representation of the initial state s with that of the state-to-state mapping  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \cdots \odot \Delta_{w_j}$  to obtain a representation for the successor state  $\Delta_{w_1} \odot \Delta_{w_2} \odot \Delta_{w_2} \odot \Delta_{w_3} \odot \Delta_{w_2} \odot \Delta_{w_3} \odot \Delta_{w_3} \odot$

We now describe a generic, though not necessarily efficient, implementation of these steps. Let  $Q = \{q_0, q_1, \dots, q_{|Q|-1}\}$  be the states of M. The state-to-state mapping  $\Delta_x$  for the FSM M needed for the first step can be represented by a  $|Q| \times |Q|$  Boolean matrix  $N(x) = \{n_{ij}(x)\}$  in which the entry in row i and column j,  $n_{ij}(x)$ , satisfies

$$n_{i,j}(x) = \left\{ \begin{array}{ll} 1 & \text{if } M \text{ moves from state } q_i \text{ to state } q_j \text{ on input } x \\ 0 & \text{otherwise} \end{array} \right.$$

Consider again the FSM shown in Fig. 3.10. The matrices associated with its four pairs of inputs  $x \in \{(0,0),(0,1),(1,0),(1,1)\}$  are shown below, where N((0,1)) = N((1,0)):

$$N((0,0)) = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \quad N((0,1)) = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

$$N((1,1)) = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

From these matrices the generic matrix N((u,v)) parameterized by the values of the inputs (a pair (u,v) in this example) is produced from the following Boolean functions:  $t=\overline{u}\wedge\overline{v}$ , the carry-terminate function,  $p=u\oplus v$ , the carry-propagate function, and  $g=u\wedge v$ , the carry-generate function.

$$N((u,v)) = \begin{bmatrix} t & p & g & 0 \\ t & p & g & 0 \\ 0 & t & p & g \\ 0 & t & p & g \end{bmatrix}$$

Let  $\sigma(i) = (0,0,\ldots,0,1,0,\ldots 0)$  be the unit |Q|-vector that has value 1 in the ith position and zeros elsewhere. Let  $\sigma(i)N(x)$  denote Boolean vector-matrix multiplication in which addition is OR and multiplication is AND. Then, for each i,  $\sigma(i)N(x) = (n_{i,1}, n_{i,2}, \ldots, n_{i,|Q|})$  is the unit vector denoting the state that M enters when it is in state  $q_i$  and receives input x.

Let  $N(x,y) = N(x) \times N(y)$  be the Boolean matrix-matrix multiplication of matrices N(x) and N(y) in which addition is OR and multiplication is AND. Then, for each x and y the entry in row i and column j of  $N(x) \times N(y)$ , namely  $n_{i,j}^{(2)}(x,y)$ , satisfies the following identity:

$$n_{i,j}^{(2)}(x,y) = \bigvee_{q_t \in Q} n_{i,t}(x) \cdot n_{t,j}(y)$$

That is,  $n_{i,j}^{(2)}(x,y)=1$  if there is a state  $q_t\in Q$  such that in state  $q_i$ , M is given input x, moves to state  $q_t$ , and then moves to state  $q_j$  on input y. Thus, the composition operator  $\odot$  can be realized through the multiplication of Boolean matrices. It is straightforward to show that matrix multiplication is associative. (See Problem 3.10.)

Since matrix multiplication is associative, a prefix computation using matrix multiplication as a composition operator for each prefix  $\boldsymbol{x}^{(j)} = (x_1, x_2, \dots, x_j)$  of the input string  $\boldsymbol{x}$  generates a matrix  $N(\boldsymbol{x}^{(j)}) = N(x_1) \times N(x_2) \times \dots \times N(x_j)$  defining the state-to-state mapping associated with  $\boldsymbol{x}^{(j)}$  for each value of  $1 \leq j \leq n$ .

The fourth step, the application of a sequence of state-to-state mappings to the initial state  $s=q_r$ , represented by the |Q|-vector  $\sigma(r)$ , is obtained through the vector-matrix multiplication  $\sigma(r)N(\boldsymbol{x^{(j)}})$  for  $1 \leq j \leq n$ .

The fifth step involves the computation of the output word from the current state. Let the column |Q|-vector  $\lambda$  contain in the tth position the output of the FSM M when in state  $q_t$ . Then, the output produced by the FSM after the jth input is the product  $\sigma(r)N(\boldsymbol{x}^{(j)})\lambda$ . This result is summarized below.

**THEOREM 3.2.2** Let the finite-state machine  $M=(\Sigma, \Psi, Q, \delta, \lambda, s, F)$  with |Q| states compute a subfunction f of  $f_M^{(T)}$  in T steps. Then f has the following size and depth bounds over the standard basis  $\Omega_0$  for some  $\kappa \geq 1$ :

$$C_{\Omega_0}(f) = O\left(M_{\text{matrix}}(|Q|, \kappa)T\right)$$

$$D_{\Omega_0}(f) = O\left((\kappa \log |Q|)(\log T)\right)$$

Here  $M_{\text{matrix}}(n, \kappa)$  is the size of a circuit to multiply two  $n \times n$  matrices with a circuit of depth  $\kappa \log n$ . These bounds can be achieved simultaneously.

**Proof** The circuits realizing the Boolean functions  $\{n_{i,j}(x) \mid 1 \leq i,j \leq |Q|\}$ , x an input, each have a size determined by the size of the input alphabet  $\Sigma$ , which is constant. The number of operations required to multiply two Boolean matrices with a circuit of depth  $\kappa \log |Q|, \kappa \geq 1$ , is  $M_{\text{matrix}}(|Q|,\kappa)$ . (See Section 6.3. Note that  $M_{\text{matrix}}(|Q|,\kappa) \leq |Q|^3$ .) Finally, the prefix circuit uses O(T) copies of the matrix multiplication circuit and has a depth of  $O(\log T)$  copies of the matrix multiplication circuit along the longest path. (See Section 2.6.)

When an FSM has a large number of states but its next-state function is relatively simple, that is, it has a size that is at worst a polynomial in  $\log |Q|$ , the above size bound will be much larger than the size bound given in Theorem 3.1.1 because  $M_{\text{matrix}}(n,\kappa)$  grows exponentially in  $\log |Q|$ . The depth bound grows linearly with  $\log |Q|$  whereas the depth of the next-state function on which the depth bound of Theorem 3.1.1 depends will typically grow either linearly or as a small polynomial in  $\log \log |Q|$  for an FSM with a relatively simple next-state function. Thus, the depth bound will be smaller than that of Theorem 3.1.1 for very large values of T, but for smaller values, the latter bound will dominate.

#### 3.2.1 A Shallow Circuit Simulating Addition

Applying the above result to the adder FSM of Fig. 3.10, we produce a circuit that accepts T pairs of binary inputs and computes the sum as T-bit binary numbers. Since this FSM has four states, the theorem states that the circuit has size O(T) and depth  $O(\log T)$ . The carry-lookahead adder of Section 2.7 has these characteristics.

We can actually produce the carry-lookahead circuit by a more careful design of the state-to-state mappings. We use the following encodings for states, where states are represented by pairs  $\{(c,s)\}$ .

| Stat  | e En | coding |  |

|-------|------|--------|--|

| q     | c    | s      |  |

| $q_0$ | 0    | 0      |  |

| $q_1$ | 0    | 1      |  |

| $q_2$ | 1    | 0      |  |

| $q_3$ | 1    | 1      |  |

Since the next-state mappings are the same for inputs 0, 1, and 1, 0, we encode an input pair (u,v) by (g,p), where  $g=u\wedge v$  and  $p=u\oplus v$  are the carry-generate and carry-propagate variables introduced in Section 2.7 and used above. With these encodings, the three different next-state mappings  $\{\Delta_{0,0},\Delta_{0,1},\Delta_{1,1}\}$  defined in Fig. 3.11 can be encoded as shown in the table below. The entry at the intersection of row (c,s) and column (p,g) in this table is the value  $(c^*,s^*)$  of the generic next-state function  $(c^*,s^*)=\Delta_{p,g}(c,s)$ . (Here we abuse notation slightly to let  $\Delta_{p,g}$  denote the state-to-state mapping associated with the pair (u,v) and represent the state q of M by the pair (c,s).)

| _ | $\begin{bmatrix} g \\ p \end{bmatrix}$ | 0 0   |       | (     | )<br>1 | 1<br>0 |       |  |

|---|----------------------------------------|-------|-------|-------|--------|--------|-------|--|

| c | s                                      | $c^*$ | $s^*$ | $c^*$ | $s^*$  | $c^*$  | $s^*$ |  |

| 0 | 0                                      | 0     | 0     | 0     | 1      | 1      | 0     |  |

| 0 | 1                                      | 0     | 0     | 0     | 1      | 1      | 0     |  |

| 1 | 0                                      | 0     | 1     | 1     | 0      | 1      | 1     |  |

| 1 | 1                                      | 0     | 1     | 1     | 0      | 1      | 1     |  |

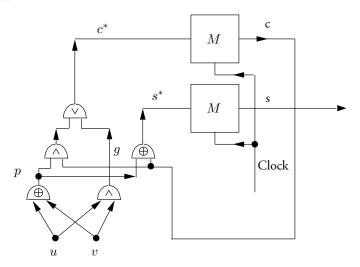

Inspection of this table shows that we can write the following formulas for  $c^*$  and  $s^*$ :

$$c^* = (p \wedge c) \vee q, \quad s^* = p \oplus c$$

Consider two successive input pairs  $(u_1,v_1)$  and  $(u_2,v_2)$  and associated pairs  $(p_1,g_1)$  and  $(p_2,g_2)$ . If the FSM of Fig. 3.10 is in state  $(c_0,s_0)$  and receives input  $(u_1,v_1)$ , it enters the state  $(c_1,s_1)=(p_1\wedge c_0\vee g_1,p_1\oplus c_0)$ . This new state can be obtained by combining  $p_1$  and  $g_1$  with  $c_0$ . Let  $(c_2,s_2)$  be the successor state when the mapping  $\Delta_{p_2,g_2}$  is applied to  $(c_1,s_1)$ . The effect of the operator  $\odot$  on successive state-to-state mappings  $\Delta_{p_1,g_1}$  and  $\Delta_{p_2,g_2}$  is shown below, in which (3.2) is used:

$$(\Delta_{p_1,g_1} \odot \Delta_{p_2,g_2})(q) = \Delta_{p_2,g_2}(\Delta_{p_1,g_1}((c_0,s_0)))$$

=  $\Delta_{p_2,g_2}(p_1 \wedge c_0 \vee g_1, p_1 \oplus c_0)$

$$= (p_2 \wedge (p_1 \wedge c_0 \vee g_1) \vee g_2, p_2 \oplus (p_1 \wedge c_0 \vee g_1))$$

=  $((p_2 \wedge p_1) \wedge c_0 \vee (g_2 \vee p_2 \wedge g_1)), p_2 \oplus (p_1 \wedge c_0 \vee g_1))$

=  $(c_2, s_2)$

It follows that  $c_2$  can be computed from  $p^* = p_2 \wedge p_1$  and  $g^* = g_2 \vee p_2 \wedge g_1$  and  $c_0$ . The value of  $s_2$  is obtained from  $p_2$  and  $c_1$ . Thus the mapping  $\Delta_{p_1,g_1} \odot \Delta_{p_2,g_2}$  is defined by  $p^*$  and  $g^*$ , quantities obtained by combining the pairs  $(p_1,g_1)$  and  $(p_2,g_2)$  using the same associative operator  $\diamond$  defined for the carry-lookahead adder in Section 2.7.1.

To summarize, the state-to-state mappings corresponding to subsequences of an input string  $((u_0,v_0),(u_1,v_1),\ldots,(u_{n-2},v_{n-2}),(u_{n-1},v_{n-1}))$  can be computed by representing this string by the carry-propagate, carry-generate string  $((p_0,g_0),(p_1,g_1),\ldots,(p_{n-2},g_{n-2}),(p_{n-1},g_{n-1}))$ , computing the prefix operation on this string using the operator  $\diamond$ , then computing  $c_i$  from  $c_0$  and the carry-propagate and carry-generate functions for the ith stage and  $s_i$  from this carry-propagate function and  $c_{i-1}$ . This leads to the carry-lookahead adder circuit of Section 2.7.1.

# 3.3 Designing Sequential Circuits

Sequential circuits are concrete machines constructed of gates and binary memory devices. Given an FSM, a sequential machine can be constructed for it, as we show.

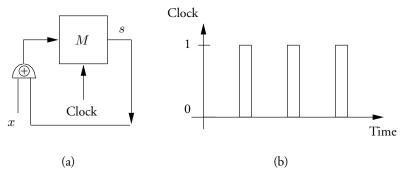

A **sequential circuit** is constructed from a logic circuit and a collection of clocked binary memory units, as suggested in Figs. 3.12(a) and 3.15. (Shown in Fig. 3.12(a) is a simple sequential circuit that computes the EXCLUSIVE OR of the initial value in memory and the external input to the sequential circuit.) Inputs to the logic circuit consist of outputs from the binary memory units as well as external inputs. The outputs of the logic circuit serve as inputs to the clocked binary memory units as well as external outputs.

A clocked binary memory unit is driven by a **clock**, a periodic signal that has value 1 (it is **high**) during short, uniformly spaced time intervals and is otherwise 0 (it is **low**), as suggested in Figs. 3.12(b). For correct operation it is assumed that the input to a memory unit does not change when the clock is high. Thus, the outputs of a logic circuit feeding the memory units cannot change during these intervals. This in turn requires that all changes in the inputs to

**Figure 3.12** (a) A sequential circuit with one gate and one clocked memory unit computing the EXCLUSIVE OR of its inputs; (b) a periodic clock pattern.

this circuit be fully propagated to its outputs in the intervals when the clock is low. A circuit that operates this way is considered **safe**. Designers of sequential circuits calculate the time for signals to pass through a logic circuit and set the interval between clock pulses to insure that the operation of the sequential circuit is safe.

Sequential circuits are designed from finite-state machines (FSMs) in a series of steps. Consider an FSM  $M=(\Sigma,\Psi,Q,\delta,\lambda,s)$  with input alphabet  $\Sigma$ , output alphabet  $\Psi$ , state set Q, next-state function  $\delta:Q\times\Sigma\mapsto Q$ , output function  $\lambda:Q\mapsto\Psi$ , and initial state s. (For this discussion we ignore the set of final states; they are important only when discussing language recognition.) We illustrate the design of a sequential machine using the FSM of Fig. 3.10, which is repeated in Fig. 3.13.

The first step in producing a sequential circuit from an FSM is to assign unique binary tuples to each input letter, output letter, and state (the state-assignment problem). This is illustrated for our FSM by the tables of Fig. 3.14 in which the identity encoding is used on inputs and outputs. This step can have a large impact on the size of the logic circuit produced. Second, tables for  $\delta: B^4 \mapsto B^2$  and  $\lambda: B^2 \mapsto B$ , the next-state and output functions of the FSM, respectively, are produced from the description of the FSM, as shown in the same figure. Here  $c^*$  and  $s^*$  represent the successor to the state (c,s). Third, circuits are designed that realize the binary functions associated with  $c^*$  and  $s^*$ . Fourth and finally, these circuits are connected to clocked binary memory devices, as shown in Fig. 3.15, to produce a sequential circuit that realizes the FSM. We leave to the reader the task of demonstrating that these circuits compute the functions defined by the tables. (See Problem 3.11.)

Since gates and clocked memory devices can be constructed from semiconductor materials, a sequential circuit can be assembled from physical components by someone skilled in the use of this technology. We design sequential circuits in this book to obtain upper bounds on the size and depth of the next-state and output functions of a sequential machine so that we can derive computational inequalities.

**Figure 3.13** A finite-state machine that simulates the ripple adder of Fig. 2.14. It is in state  $q_r$  if the carry-and-sum pair  $(c_{j+1}, s_j)$  generated by the jth full adder of the ripple adder represents the integer r,  $0 \le r \le 3$ . The output produced is the sum bit.

| Input.              | Encod | ling           |              | Outp             | ut En | cod         | ing   |     | Sta          | ite En | coding |

|---------------------|-------|----------------|--------------|------------------|-------|-------------|-------|-----|--------------|--------|--------|

| $\sigma \in \Sigma$ | u     | $\overline{v}$ | )            | $\lambda(q) \in$ | Ψ     | $\lambda$ ( | (q)   |     | q            | c      | s      |

| 0 0                 | 0     | 0              |              | 0                |       | 0           |       |     | $q_0$        | 0      | 0      |

| 0 1                 | 0     | 1              |              | 1                |       | 1           |       |     | $q_1$        | 0      | 1      |

| 1 0<br>1 1          | 1     | 0              |              |                  | •     |             |       |     | $q_2$        | 1      | 0      |

| 1 1                 | 1     | 1              |              |                  |       |             |       |     | $q_3$        | 1      | 1      |

|                     |       | $\delta: B$    | $^4 \mapsto$ | _                |       |             |       | _   | $^2 \mapsto$ | B      |        |

| (                   | c $s$ | u              | v            | $c^*$            | $s^*$ | _           | $c^*$ | ٤   | 3*           | s      |        |

| _                   | ) (   | Λ              | Λ            | Λ                | Λ     | _           | Λ     | - ( | )            | Λ      |        |

|   | δ | : B | $^4 \mapsto$ | $B^2$ |       |   |       | $B^2 \vdash$ | $\rightarrow B$ |

|---|---|-----|--------------|-------|-------|---|-------|--------------|-----------------|

| c | s | u   | v            | $c^*$ | $s^*$ | - | $c^*$ | $s^*$        | s               |

| 0 | 0 | 0   | 0            | 0     | 0     | - | 0     | 0            | 0               |

| 0 | 1 | 0   | 0            | 0     | 0     |   | 0     | 1            | 1               |

| 1 | 0 | 0   | 0            | 0     | 1     |   | 1     | 0            | 0               |

| 1 | 1 | 0   | 0            | 0     | 1     |   | 1     | 1            | 1               |

| 0 | 0 | 0   | 1            | 0     | 1     |   |       |              | •               |

| 0 | 1 | 0   | 1            | 0     | 1     |   |       |              |                 |

| 1 | 0 | 0   | 1            | 1     | 0     |   |       |              |                 |

| 1 | 1 | 0   | 1            | 1     | 0     |   |       |              |                 |

| 0 | 0 | 1   | 0            | 0     | 1     |   |       |              |                 |

| 0 | 1 | 1   | 0            | 0     | 1     |   |       |              |                 |

| 1 | 0 | 1   | 0            | 1     | 0     |   |       |              |                 |

| 1 | 1 | 1   | 0            | 1     | 0     |   |       |              |                 |

| 0 | 0 | 1   | 1            | 1     | 0     |   |       |              |                 |

| 0 | 1 | 1   | 1            | 1     | 0     |   |       |              |                 |

| 1 | 0 | 1   | 1            | 1     | 1     |   |       |              |                 |

| 1 | 1 | 1   | 1            | 1     | 1     |   |       |              |                 |

**Figure 3.14** Encodings for inputs, outputs, states, and the next-state and output functions of the FSM adder.

**Figure 3.15** A sequential circuit for the FSM that adds binary numbers.

#### 3.3.1 Binary Memory Devices

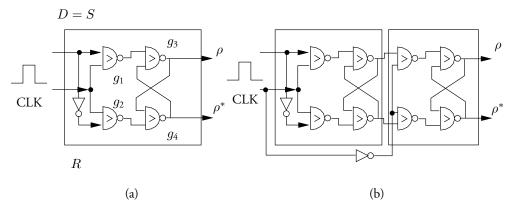

It is useful to fix ideas about memory units by designing one (a latch) from logic gates. We use two latchs to create a flip-flop, the standard binary storage device. A collection of clocked flip-flops is called a **register**. A clocked **latch** can be constructed from a few AND and NOT gates, as shown in Fig. 3.16(a). The NAND gates (they compute NOT of AND) labeled  $g_3$  and  $g_4$  form the heart of the latch. Consider the inputs to  $g_3$  and  $g_4$ , the lines connected to the outputs of NAND gates  $g_1$  and  $g_2$ . If one is set to 1 and the other reset to 0, after all signals settle down,  $\rho$  and  $\rho^*$  will assume complementary values (one will have value 1 and the other will have value 0), regardless of their previous values. The gate with input 1 will assume output 0 and vice versa.

Now if the outputs of  $g_1$  and  $g_2$  are both set to 1 and the values previously assumed by  $\rho$  and  $\rho^*$  are complementary, these values will be retained due to the feedback between  $g_3$  and  $g_4$ , as the reader can verify. Since the outputs of  $g_1$  and  $g_2$  are both 1 when the clock input (CLK in Fig. 3.16) has value 0, the complementary outputs of  $g_3$  and  $g_4$  remain unchanged when the clock is low. Since the outputs of a latch provide inputs to the logic-circuit portion of a sequential circuit, it is important that the latch outputs remain constant when the clock is low.

When the clock input is 1, the outputs of  $g_1$  and  $g_2$  are  $\overline{S}$  and  $\overline{R}$ , the Boolean complements of S and R. If S and R are complementary, as is true for this latch since  $R = \overline{S}$ , this device will store the value of S in  $\rho$  and its complement in  $\rho^*$ . Thus, if S = 1, the latch is **set** to 1, whereas if R = 1 (and S = 0) it is **reset** to 0. This type of device is called a **D-type latch**. For this reason we change the name of the external input to this memory device from S to D.

Because the output of the D-type latch shown in Fig. 3.16(a) changes when the clock pulse is high, it cannot be used as a stable input to a logic circuit that feeds this or another such flip-flop. Adding another stage like the first but having the complementary value for the clock pulse, as shown in Fig. 3.16(b), causes the output of the second stage to change only while the clock pulse is low. The output of the first stage does change when the clock pulse is high to record the new value of the state. This is called a **master-slave edge-triggered flip-flop.** Other types of flip-flop are described in texts on computer architecture.

**Figure 3.16** (a) Design of a D-type latch from NAND gates. (b) A master-slave edge-triggered D-type flip-flop.

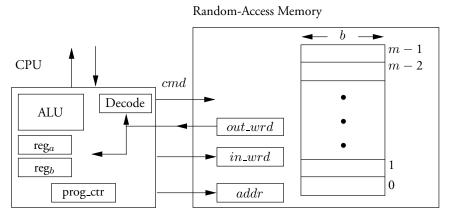

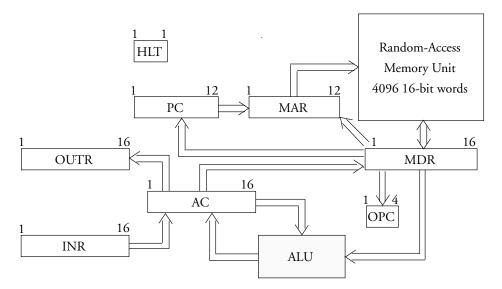

#### 3.4 Random-Access Machines

The **random-access machine** (RAM) models the essential features of the traditional serial computer. The RAM is modeled by two synchronous interconnected FSMs, a central processing unit (CPU) and a random-access memory. (See Fig. 3.17.) The CPU has a small number of storage locations called **registers** whereas the random-access memory has a large number. All operations performed by the CPU are performed on data stored in its registers. This is done for efficiency; no increase in functionality is obtained by allowing operations on data stored in memory locations as well.

#### 3.4.1 The RAM Architecture

The CPU implements a **fetch-and-execute cycle** in which it alternately reads an instruction from a program stored in the random-access memory (the **stored-program concept**) and executes it. Instructions are read and executed from consecutive locations in the random-access memory unless a **jump instruction** is executed, in which case an instruction from a non-consecutive location is executed next.

A CPU typically has five basic kinds of instruction: a) arithmetic and logical instructions of the kind described in Sections 2.5.1, 2.7, 2.9, and 2.10, b) memory load and store instructions for moving data between memory locations and registers, c) jump instructions for breaking out of the current program sequence, d) input and output (I/O) instructions, and e) a halt instruction.

The basic random-access memory has an output word  $(out\_wrd)$  and three input words, an address (addr), a data word  $(in\_wrd)$ , and a command (cmd). The command specifies one of three actions, a) read from a memory location, b) write to a memory location, or c) do nothing. Reading from address addr deposits the value of the word at this location into  $out\_wrd$  whereas writing to addr replaces the word at this address with the value of  $in\_wrd$ .

**Figure 3.17** The random-access machine has a central processing unit (CPU) and a random-access memory unit.

This memory is called random-access because the time to access a word is the same for all words. The Turing machine introduced in Section 3.7 has a tape memory in which the time to access a word increases with its distance from the tape head.

The random-access memory in the model in Fig. 3.17 has  $m=2^{\mu}$  storage locations each containing a b-bit word, where  $\mu$  and b are integers. Each word has a  $\mu$ -bit address and the addresses are consecutive starting at zero. The combination of this memory and the CPU described above is the **bounded-memory RAM**. When no limit is placed on the number and size of memory words, this combination defines the **unbounded-memory RAM**. We use the term RAM for these two machines when context unambiguously determines which is intended.

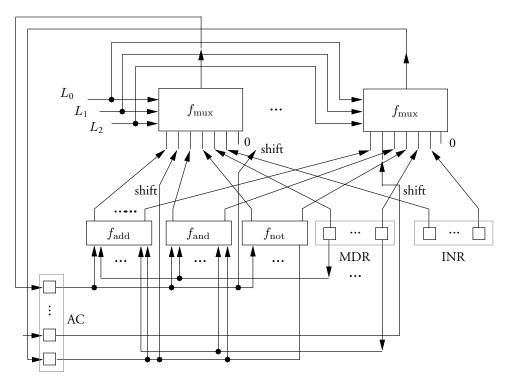

**DESIGN OF A SIMPLE CPU** The design of a simple CPU is given in Section 3.10. (See Fig. 3.31.) This CPU has eight registers, a **program counter** (PC), **accumulator** (AC), **memory address register** (MAR), **memory data register** (MDR), **operation code (opcode) register** (OPC), **input register** (INR), **output register** (OUTR), and **halt register** (HALT). Each operation that requires two operands, such as addition or vector AND, uses AC and MDR as sources for the operands and places the result in AC. Each operation with one operand, such as the NOT of a vector, uses AC as both source and destination for the result. PC contains the address of the next instruction to be executed. Unless a jump instruction is executed, PC is incremented on the execution of each instruction. If a jump instruction is executed, the value of PC is changed. Jumps occur in our simple CPU if AC is zero.

To fetch the next instruction, the CPU copies PC to MAR and then commands the random-access memory to read the word at the address in MAR. This word appears in MDR. The portion of this word containing the identity of the opcode is transferred to OPC. The CPU then inspects the value of OPC and performs the small local operations to execute the instruction represented by it. For example, to perform an addition it commands the arithmetic/logical unit (ALU) to combine the contents of MDR and AC in an adder circuit and deposit the result in AC. If the instruction is a *load accumulator* instruction (LDA), the CPU treats the bits other than opcode bits as address bits and moves them to the MAR. It then commands the random-access memory to deposit the word at this address in MDR, after which it moves the contents of MDR to AC. In Section 3.4.3 we illustrate programming in an assembly language, the language of a machine enhanced by mnemonics and labels. We further illustrate assembly-language programming in Section 3.10.4 for the instruction set of the machine designed in Section 3.10.

## 3.4.2 The Bounded-Memory RAM as FSM

As this discussion illustrates, the CPU and the random-access memory are both finite-state machines. The CPU receives input from the random-access memory as well as from external sources. Its output is to the memory and the output port. Its state is determined by the contents of its registers. The random-access memory receives input from and produces output to the CPU. Its state is represented by an m-tuple  $(w_0, w_1, \ldots, w_{m-1})$  of b-bit words, one per memory location, as well as by the values of  $in\_wrd$ ,  $out\_word$ , and addr. We say that the random-access memory has a **storage capacity** of S = mb bits. The RAM has input and output registers (not shown in Fig. 3.17) through which it reads external inputs and produces external outputs.

As the RAM example illustrates, some FSMs are programmable. In fact, a program stored in the RAM memory selects one of very many state sequences that the RAM may execute. The

Models of Computation

number of states of a RAM can be very large; just the random-access memory alone has more than  $2^S$  states.

The programmability of the unbounded-memory RAM makes it universal for FSMs, as we show in Section 3.4.4. Before taking up this subject, we pause to introduce an assembly-language program for the unbounded-memory RAM. This model will play a role in Chapter 5.

#### 3.4.3 Unbounded-Memory RAM Programs

We now introduce **assembly-language programs** to make concrete the use of the RAM. An assembly language contains one instruction for each machine-level instruction of a CPU. However, instead of bit patterns, it uses mnemonics for opcodes and labels as symbolic addresses. Labels are used in *jump* instructions.

Figure 3.18 shows a simple assembly language. It implements all the instructions of the CPU defined in Section 3.10 and vice versa if the CPU has a sufficiently long word length.

Our new assembly language treats all memory locations as equivalent and calls them registers. Thus, no distinction is made between the memory locations in the CPU and those in the random-access memory. Such a distinction is made on real machines for efficiency: it is much quicker to access registers internal to a CPU than memory locations in an external random-access memory.

Registers are used for data storage and contain integers. Register names are drawn from the set  $\{R_0, R_1, R_2, \ldots\}$ . The **address of register**  $R_i$  is i. Thus, both the number of registers and their size are potentially unlimited. All registers are initialized with the value zero. Registers used as **input registers** to a program are initialized to input values. Results of a computation are placed in **output registers**. Such registers may also serve as input registers. Each instruction may be given a **label** drawn from the set  $\{N_0, N_1, N_2, \ldots\}$ . Labels are used by jump instructions, as explained below.

| Instruction             | Meaning                                                                               |

|-------------------------|---------------------------------------------------------------------------------------|

| $\overline{INC R_i}$    | Increment the contents of $R_i$ by 1.                                                 |

| DEC $R_i$               | Decrement the contents of $R_i$ by 1.                                                 |

| CLR $R_i$               | Replace the contents of $R_i$ with 0.                                                 |

| $R_i \leftarrow R_j$    | Replace the contents of $R_i$ with those of $R_j$ .                                   |

| $JMP_+ N_i$             | Jump to closest instruction above current one with label $N_i$ .                      |

| $JMP_{-}N_{i}$          | Jump to closest instruction below current one with label $N_i$ .                      |

| $R_j \text{ JMP}_+ N_i$ | If $R_j$ contains 0, jump to closest instruction above current one with label $N_i$ . |

| $R_j$ JMP $$ $N_i$      | If $R_j$ contains 0, jump to closest instruction below current one with label $N_i$ . |

| CONTINUE                | Continue to next instruction; halt if none.                                           |

Figure 3.18 The instructions in a simple assembly language.

The meaning of each instruction should be clear except possibly for the CONTINUE and JUMP. If the program reaches a CONTINUE statement other than the last CONTINUE, it executes the following instruction. If it reaches the last CONTINUE statement, the program halts.

The jump instructions  $R_j$  JMP<sub>+</sub>  $N_i$ ,  $R_j$  JMP<sub>-</sub>  $N_i$ , JMP<sub>+</sub>  $N_i$ , and JMP<sub>-</sub>  $N_i$  cause a break in the program sequence. Instead of executing the next instruction in sequence, they cause jumps to instructions with labels  $N_i$ . In the first two cases these jumps occur only when the content of register  $R_j$  is zero. In the last two cases, these jumps occur unconditionally. The instructions with JMP<sub>+</sub> (JMP<sub>-</sub>) cause a jump to the closest instruction with label  $N_i$  above (below) the current instruction. The use of the suffixes + and - permit the insertion of program fragments into an existing program without relabeling instructions.

A **RAM program** is a finite sequence of assembly language instructions terminated with CONTINUE. A valid program is one for which each jump is to an existing label. A **halting program** is one that halts.

**TWO RAM PROGRAMS** We illustrate this assembly language with the two simple programs shown in Fig. 3.19. The first adds two numbers and the second uses the first to square a number. The heading of each program explains its operation. Registers  $R_0$  and  $R_1$  contain the initial values on which the addition program operates. On each step it increments  $R_0$  by 1 and decrements  $R_1$  by 1 until  $R_1$  is 0. Thus, on completion, the value of  $R_0$  is its original value plus the value of  $R_1$  and  $R_1$  contains 0.

The squaring program uses the addition program. It makes three copies of the initial value x of  $R_0$  and stores them in  $R_1$ ,  $R_2$ , and  $R_3$ . It also clears  $R_0$ .  $R_2$  will be used to reset  $R_1$  to x after adding  $R_1$  to  $R_0$ .  $R_3$  is used as a counter and decremented x times, after which x is added to zero x times in  $R_0$ ; that is,  $x^2$  is computed.

| R     | $_0 \leftarrow R_0 + R_1$                                            | Comments                            |                | $R_0 \leftarrow R_0^2$                                                                                     | Comments                                                   |

|-------|----------------------------------------------------------------------|-------------------------------------|----------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| $N_0$ | R <sub>1</sub> JMP <sub>-</sub> N <sub>1</sub><br>INC R <sub>0</sub> | End if $R_1 = 0$<br>Increment $R_0$ |                | $R_2 \leftarrow R_0 \\ R_3 \leftarrow R_0$                                                                 | Copy $R_0$ ( $x$ ) to $R_2$<br>Copy $R_0$ ( $x$ ) to $R_3$ |

|       | $DEC R_1$                                                            | Decrement R <sub>1</sub>            |                | $CLR R_0$                                                                                                  | Clear the contents of $R_0$                                |

|       | $JMP_+ N_0$                                                          | Repeat                              | $N_2$          | $R_1 \leftarrow R_2$                                                                                       | Copy $R_2(x)$ to $R_1$                                     |

| $N_1$ | CONTINUE                                                             |                                     | N <sub>0</sub> | $\begin{array}{c} R_1 \ JMP \ N_1 \\ INC \ R_0 \\ DEC \ R_1 \\ JMP_+ \ N_0 \\ CONTINUE \end{array}$        | $R_0 \leftarrow R_0 + R_1$                                 |

|       |                                                                      |                                     | $N_3$          | DEC R <sub>3</sub> R <sub>3</sub> JMP <sub>-</sub> N <sub>3</sub> JMP <sub>+</sub> N <sub>2</sub> CONTINUE | Decrement $R_3$<br>End when zero<br>Add $x$ to $R_0$       |

**Figure 3.19** Two simple RAM programs. The first adds two integers stored initially in registers  $R_0$  and  $R_1$ , leaving the result in  $R_0$ . The second uses the first to square the contents of  $R_0$ , leaving the result in  $R_0$ .

As indicated above, with large enough words each of the above assembly-language instructions can be realized with a few instructions from the instruction set of the CPU designed in Section 3.10. It is also true that each of these CPU instructions can be implemented by a fixed number of instructions in the above assembly language. That is, with sufficiently long memory words in the CPU and random-access memory, the two languages allow the same computations with about the same use of time and space.

However, the above assembly-language instructions are richer than is absolutely essential to perform all computations. In fact with just five assembly-language instructions, namely INC, DEC, CONTINUE,  $R_j$  JMP $_+$   $N_i$ , and  $R_j$  JMP $_ N_i$ , all the other instructions can be realized. (See Problem 3.21.)

#### 3.4.4 Universality of the Unbounded-Memory RAM

The unbounded-memory RAM is universal in two senses. First, it can simulate any finite-state machine including another random-access machine, and second, it can execute any RAM program.

**DEFINITION 3.4.1** A machine M is universal for a class of machines C if every machine in C can be simulated by M. (A stronger definition requiring that M also be in C is used in Section 3.8.)

We now show that the RAM is universal for the class  $\mathcal C$  of finite-state machines. We show that in O(T) steps and with constant storage capacity S the RAM can simulate T steps of any other FSM. Since any random-access machine that uses a bounded amount of memory can be described by a logic circuit such as the one defined in Section 3.10, it can also be simulated by the RAM.

**THEOREM 3.4.1** Every T-step FSM  $M = (\Sigma, \Psi, Q, \delta, \lambda, s, F)$  computation can be simulated by a RAM in O(T) steps with constant space. Thus, the RAM is universal for finite-state machines.

**Proof** We sketch a proof. Since an FSM is characterized completely by its next-state and output functions, both of which are assumed to be encoded by binary functions, it suffices to write a fixed-length RAM program to perform a state transition, generate output, and record the FSM state in the RAM memory using the tabular descriptions of the next-state and output functions. This program is then run repeatedly. The amount of memory necessary for this simulation is finite and consists of the memory to store the program plus one state (requiring at least  $\log_2 |Q|$  bits). While the amount of storage and time to record and compute these functions is constant, they can be exponential in  $\log_2 |Q|$  because the next-state and output functions can be a complex binary function. (See Section 2.12.) Thus, the number of steps taken by the RAM per FSM state transition is constant.

The second notion of universality is captured by the idea that the RAM can execute RAM programs. We discuss two execution models for RAM programs. In the first, a RAM program is stored in a private memory of the RAM, say in the CPU. The RAM alternates between reading instructions from its private memory and executing them. In this case the registers described in Section 3.4.3 are locations in the random-access memory. The program counter either advances to the next instruction in its private memory or jumps to a new location as a result of a jump instruction.

In the second model (called by some [10] the **random-access stored program machine** (**RASP**)), a RAM program is stored in the random-access memory itself. A RAM program

can be translated to a RASP program by replacing the names of RAM registers by the names of random-access memory locations not used for storing the RAM program. The execution of a RASP program directly parallels that of the RAM program; that is, the RASP alternates between reading instructions and executing them. Since we do not consider the distinction between RASP and RAM significant, we call them both the RAM.

# 3.5 Random-Access Memory Design

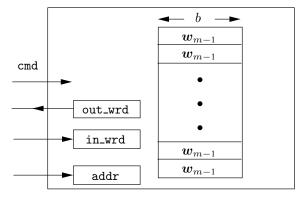

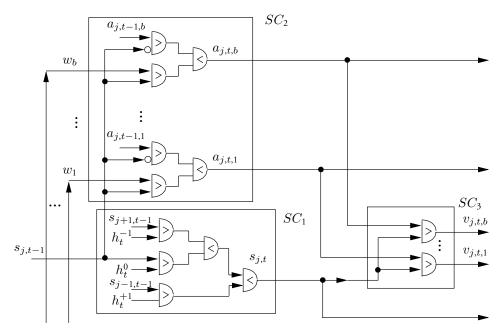

In this section we model the random-access memory described in Section 3.4 as an FSM  $M_{\rm RMEM}(\mu,b)$  that has  $m=2^{\mu}$  b-bit data words,  $w_0,w_1,\ldots,w_{m-1}$ , as well as an input data word d (in\_wrd), an input address a (addr), and an output data word z (out\_wrd). (See Fig. 3.20.) The state of this FSM is the concatenation of the contents of the data, input and output words, input address, and the command word. We construct an efficient logic circuit for its next-state and transition function.

To simplify the design of the FSM  $M_{\rm RMEM}$  we use the following encodings of the three input commands:

| Name  | $s_1$ | $s_0$ |

|-------|-------|-------|

| no-op | 0     | 0     |

| read  | 0     | 1     |

| write | 1     | 0     |

An input to  $M_{\rm RMEM}$  is a binary  $(\mu+b+2)$ -bit binary tuple, two bits to represent a command,  $\mu$  bits to specify an address, and b bits to specify a data word. The output function of  $M_{\rm RMEM}$ ,  $\lambda_{\rm RMEM}$ , is a simple projection operator and is realized by a circuit without any gates. Applied to the state vector, it produces the output word.

We now describe a circuit for  $\delta_{\rm RMEM}$ , the next-state function of  $M_{\rm RMEM}$ . Memory words remain unchanged if either **no-op** or **read** commands are executed. In these cases the value of the command bit  $s_1$  is 0. One memory word changes if  $s_1=1$ , namely, the one whose

**Figure 3.20** A random-access memory unit  $M_{\rm RMEM}$  that holds m b-bit words. Its inputs consist of a command (cmd), an input word (in\_wrd), and an address (addr). It has one output word (out\_wrd).

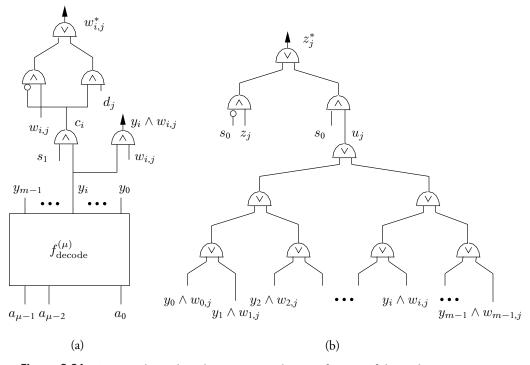

address is a. Thus, the memory words  $w_0, w_1, \ldots, w_{m-1}$  change only when  $s_1 = 1$ . The word that changes is determined by the  $\mu$ -bit address a supplied as part of the input. Let  $a_{\mu-1}, \ldots, a_1, a_0$  be the  $\mu$  bits of a. Let these bits be supplied as inputs to an  $\mu$ -bit decoder function  $f_{\text{decode}}^{(\mu)}$  (see Section 2.5.4). Let  $y_{m-1}, \ldots, y_1, y_0$  be the m outputs of a decoder circuit. Then, the Boolean function  $c_i = s_1 y_i$  (shown in Fig. 3.21(a)) is 1 exactly when the input address a is the binary representation of the integer i and the FSM  $M_{\text{RMEM}}$  is commanded to **write** the word a at address a.

Let  $\boldsymbol{w}_0^*, \boldsymbol{w}_1^*, \dots, \boldsymbol{w}_{m-1}^*$  be the new values for the memory words. Let  $w_{i,j}^*$  and  $w_{i,j}$  be the jth components of  $\boldsymbol{w}_i^*$  and  $\boldsymbol{w}_i$ , respectively. Then, for  $0 \le i \le m-1$  and  $0 \le j \le b-1$  we write  $w_{i,j}^*$  in terms of  $w_{i,j}$  and the jth component  $d_j$  of  $\boldsymbol{d}$  as follows:

$$c_i = s_1 y_i$$

$$w_{i,j}^* = \overline{c}_i w_{i,j} \lor c_i d_j$$

Figures 3.21(a) and (b) show circuits described by these formulas. It follows that changes to memory words can be realized by a circuit containing  $C_{\Omega}\left(f_{\text{decode}}^{(\mu)}\right)$  gates for the decoder, m gates to compute all the terms  $c_i$ ,  $0 \le i \le m-1$ , and 4mb gates to compute  $w_{i,j}^*$ ,  $0 \le i \le m-1$ ,  $0 \le j \le b-1$  (NOTs are counted). Combining this with Lemma 2.5.4, we have that

**Figure 3.21** A circuit that realizes the next-state and output function of the random-access memory. The circuit in (a) computes the next values  $\{w_{i,j}^*\}$  for components of memory words, whereas that in (b) computes components  $\{z_i^*\}$  of the output word. The output  $y_j \wedge w_{i,j}$  of (a) is an input to (b).

a circuit realizing this portion of the next-state function has at most  $m(4b+2)+(2\mu-2)\sqrt{m}$  gates. The depth of this portion of the circuit is the depth of the decoder plus 4 because the longest path between an input and an output  $\boldsymbol{w}_0^*, \boldsymbol{w}_1^*, \ldots, \boldsymbol{w}_{m-1}^*$  is through the decoder and then through the gates that form  $\overline{c}_i w_{i,j}$ . This depth is at most  $\lceil \log_2 \mu \rceil + 5$ .

The circuit description is complete after we give a circuit to compute the output word z. The value of z changes only when  $s_0 = 1$ , that is, when a **read** command is issued. The jth component of z, namely  $z_j$ , is replaced by the value of  $w_{i,j}$ , where i is the address specified by the input a. Thus, the new value of  $z_j$ ,  $z_j^*$ , can be represented by the following formula (see the circuit of Fig. 3.21(b)):

$$z_j^* = \overline{s}_0 z_j \vee s_0 \left( \bigvee_{k=0}^{m-1} y_k w_{k,j} \right) \qquad \text{for } 0 \le j \le b-1$$