|

Research on Computational Nanotechnology

|

Publications†Stochastic Assembly of Sublithographic Nanoscale Interfaces 1, André DeHon, Patrick Lincoln, John E. Savage IEEE Transactions in Nanotechnology, September 2003.Sub-lithographic Semiconductor Computing Systems, André DeHon describing work with Charles M. Lieber, Patrick Lincoln, and John E. Savage, HotChips 15 (HotChips-15, August 17--19, 2003).Decoding of Stochastically Assembled Nanoarrays1, Benjamin Gojman, Eric Rachlin, and John E. Savage, Proceedings of the IEEE 2004 Int. Symp. on VLSI, pp. 11-18, February 19-20, 2004.Analysis of a Mask-Based Decoder1, Eric Rachlin, John E. Savage, and Benjamin Gojman, Proceedings of the IEEE Computer Society Annl. Symp. on VLSI, A. Smailagic and N. Ranganathan (Eds.), May 11-12, 2005, pp. 6-13.Efficient Data Storage in Large Nanoarrays, Lee-Ad Gottlieb, John E. Savage, and Arkady Yerukhimovich, Theory of Computing Systems, Vol. 38, pp. 503-536, 2005.Evaluation of Design Strategies for Stochastically Assembled Nanoarray Memories2, Benjamin Gojman, Eric Rachlin, and John E. Savage, ACM J. on Emerging Technologies in Computing Systems, Vol. 1, No. 2, pp. 73-108, July 2005.Nanowire Addressing in the Face of Uncertainty1, Eric Rachlin and John E. Savage, Proceedings of the IEEE 2006 Int. Symp. on VLSI, March 2-3, 2006.Radial Addressing of Nanowires2, John E. Savage, Eric Rachlin, André DeHon, Charles M. Lieber, and Yue Wu, October 6, 2005, ACM J. on Emerging Technologies in Computing Systems, Vol. 2, No. 2, pp.129-154, April, 2006.Nanowire Addressing with Randomized-Contact Decoders1, Eric Rachlin, John E. Savage, Procs. IEEE/ACM Int. Conf. on Computer-Aided Design (ICCAD), pp. 735-742, 2006.Analysis of Mask-Based Nanowire Decoders 1, Eric Rachlin, John E. Savage, IEEE Transactions on Computers, Vol. 57, No. 2, pp. 175-187, 2008.Modeling and Analysis of a Membrane-Based Randomized-Contact Decoder, Jennifer Long, John E. Savage, Procs. NSTI-Nanotech 2008, Vol. 3, pp. 80-83, June 1-5, 2008. |

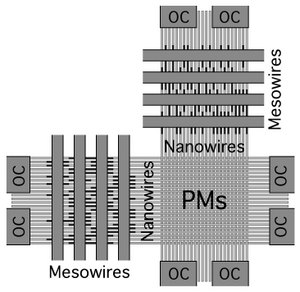

Nanowire-based crossbar A Framework for Coded Computation 1, Eric Rachlin, John E. Savage, Procs. IEEE International Symposium on Information Theory, pp. 2342-2346, July 6-11, 2008.Nanowire Addressing with Randomized-Contact Decoders

,

Eric Rachlin, John E. Savage, Theoretical Computer Science, Vol. 408, Issues

2-3, pp. 241-261, October, 2008.

y

|

|

†

This research was supported in part by NSF NIRT Grant

CCR-0210225 and NSF NER Grant CCF-0403674.

|